# **M10**

# **Quectel Cellular Engine**

# Hardware Design Application Notes

M10\_HD\_AN01\_V1.02

| <b>Document Title</b>                 | M10 Hardware Design Application Notes |  |

|---------------------------------------|---------------------------------------|--|

| Version                               | 1.02                                  |  |

| Date                                  | 2010-05-30                            |  |

| Status                                | Release                               |  |

| Document Control ID M10_HD_AN01_V1.02 |                                       |  |

#### **General Notes**

Quectel offers this information as a service to its customers, to support application and engineering efforts that use the products designed by Quectel. The information provided is based upon requirements specifically provided for Quectel by the customers. Quectel has not undertaken any independent search for additional relevant information, including any information that may be in the customer's possession. Furthermore, system validation of this product designed by Quectel within a larger electronic system remains the responsibility of the customer or the customer's system integrator. All specifications supplied herein are subject to change.

#### Copyright

This document contains proprietary technical information which is the property of Quectel Limited, copying of this document and giving it to others and the using or communication of the contents thereof, are forbidden without express authority. Offenders are liable to the payment of damages. All rights reserved in the event of grant of a patent or the registration of a utility model or design. All specification supplied herein are subject to change without notice at any time.

Copyright © Quectel Wireless Solutions Co., Ltd. 2010

M10 HD AN01 V1.02 -1-

# **Contents**

| 0. Revision History                               | 5  |

|---------------------------------------------------|----|

| 1. Introduction                                   | 6  |

| 1.1. Related Documents                            | 6  |

| 1.2. Terms and Abbreviations                      | 6  |

| 2. Product Concept                                | 7  |

| 3. Placement                                      | 8  |

| 3.1. Pin Assignment                               | 8  |

| 3.2. Placement Recommendation                     | 9  |

| 3.3. Placement Clearance                          | 9  |

| 4. Digital I/O Connection                         | 11 |

| 5. VDD_EXT & STATUS Pin                           | 12 |

| 6. Serial Port and Debug Port                     | 13 |

| 7. SIM Card                                       | 14 |

| 8. SLEEP Mode                                     |    |

| 9. Audio Trace                                    |    |

| 10. RF Design Guide                               |    |

| 10.1. Recommended Impedance Matching Circuit      | 17 |

| 10.2. Matched RF Transmission Line Design         | 18 |

| 10.3. PCB Layout Consideration                    | 19 |

| 11 The Recommended Ramn-soak-spike Reflow Profile | 22 |

# **Table Index**

| TABLE 1: RELATED DOCUMENTS                      | 6  |

|-------------------------------------------------|----|

| TABLE 2: TERMS AND ABBREVIATIONS                | 6  |

| TABLE 3: DIGITAL I/O ELECTRICAL CHARACTERISTICS | 11 |

| TABLE 4: STACK-UP OF THE FOUR-LAYER PCB         | 21 |

# Figure Index

| FIGURE 1: PIN ASSIGNMENT                                              | 8  |

|-----------------------------------------------------------------------|----|

| FIGURE 2: RECOMMENDATION OF PLACEMENT                                 | 9  |

| FIGURE 3: PLACEMENT CLEARANCE                                         | 10 |

| FIGURE 4: CIRCUIT OF THE SIM CARD                                     | 14 |

| FIGURE 5: AUDIO TRACE ROUTING EXAMPLE                                 | 16 |

| FIGURE 6: T-TYPE MATCHING CIRCUIT                                     | 17 |

| FIGURE 7: Π-TYPE MATCHING CIRCUIT                                     |    |

| FIGURE 8: M10 RF_ANT PCB LAYOUT                                       | 18 |

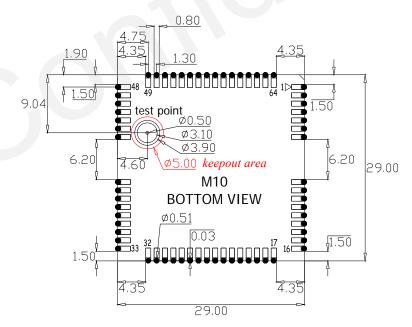

| FIGURE 9: M10 BOTTOM DIMENSIONS                                       | 19 |

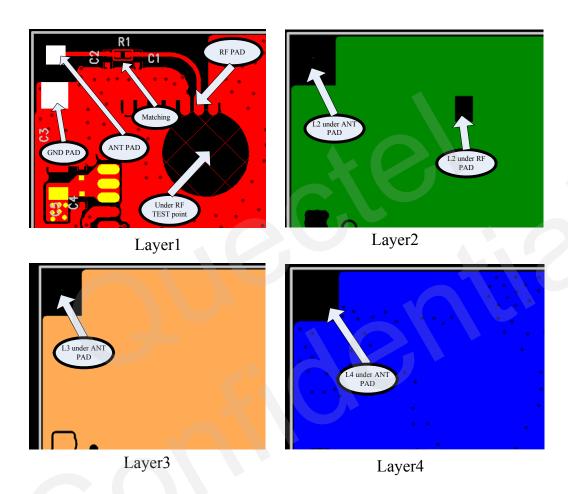

| FIGURE 10: REFERENCE PCB DESIGN WITH ANTENNA PAD IN A FOUR-LAYER PCB  | 20 |

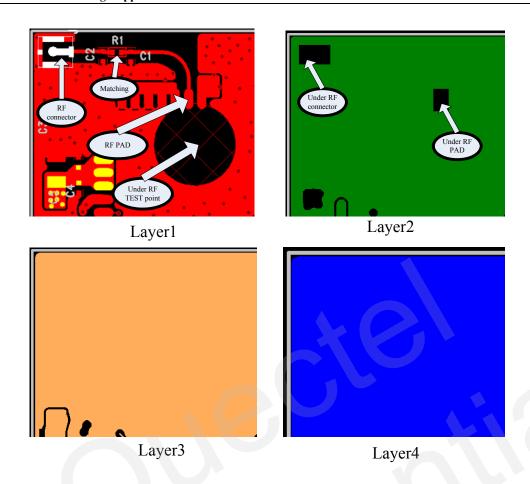

| FIGURE 11: REFERENCE PCB DESIGN WITH RF CONNECTOR IN A FOUR-LAYER PCB | 2  |

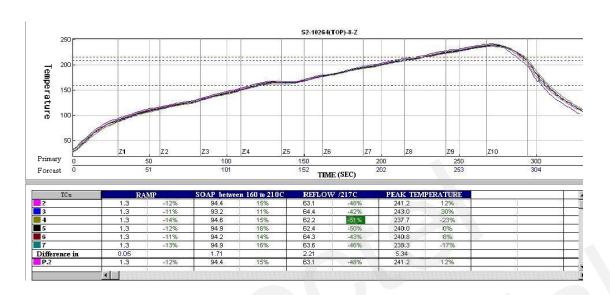

| FIGURE 12: THE RECOMMENDED RAMP-SOAK-SPIKE REFLOW PROFILE             | 22 |

- 5 -

# 0. Revision History

| Revision | Date       | Author               | Description of change                    |

|----------|------------|----------------------|------------------------------------------|

| 1.00     | 2009-06-25 | Ken JI / Samuel HONG | Initial                                  |

| 1.01     | 2010-02-25 | Tracy ZHANG          | Modify Figure 1 and Figure 9             |

| 1.02     | 2010-05-30 | Yong An              | 1.Add STATUS pin and its function        |

|          |            |                      | description                              |

|          |            |                      | 2. Disable VDD_EXT pin as the indication |

|          |            |                      | of power-on and power-down.              |

# 1. Introduction

This document gives recommendation for Quectel's M10 module integration in a wireless application, such as vehicle tracking system, smart metering and PDA. It gives some recommendations for design notes, reference circuit and PCB layout.

#### 1.1. Related Documents

**Table 1: Related documents**

| SN  | Document name       | Remark                                 |  |

|-----|---------------------|----------------------------------------|--|

| [1] | M10_HD              | Hardware design document of M10 module |  |

| [2] | GSM_UART_AN         | GSM module UART port application note  |  |

| [3] | GSM_AUDIO_UGD       | GSM module audio design user guide     |  |

| [4] | GSM_FW_Upgrade_AN01 | GSM Firmware upgrade application note  |  |

### 1.2. Terms and Abbreviations

**Table 2: Terms and abbreviations**

| Abbreviation | Description                                     |  |

|--------------|-------------------------------------------------|--|

| GPRS         | General Packet Radio Service                    |  |

| GSM          | Global System for Mobile communications         |  |

| PCB          | Printed Circuit Board                           |  |

| RF           | Radio Frequency                                 |  |

| SMD          | Surface Mounted Devices                         |  |

| SMT          | Surface Mount Technology                        |  |

| TCP/IP       | Transmission Control Protocol/Internet Protocol |  |

# 2. Product Concept

The M10 is a Quad-band GSM/GPRS engine that works at frequency bands of GSM850, EGSM 900, DCS1800 and PCS 1900. The M10 features GPRS multi-slot class 12(default)/ class 10/class8 and supports the GPRS coding schemes CS-1, CS-2, CS-3 and CS-4.

The M10 is an SMD type module with 64-pin pads and a tiny profile of 29mm x 29mm x 3. 6 mm (the thickness of PCB is 1.6mm), which can fit into almost all customers' applications. It provides all hardware interfaces between the module and customer's host board.

- External controller can communicate with M10 through its main UART port.

- Two audio channels include two microphone inputs and two speaker outputs, which can be easily configured by AT commands.

The module is designed with power saving technique so that the current consumption could be as low as 0.7mA in SLEEP mode.

TCP/IP and some other Internet protocol stacks have been integrated in the module.

The module is fully RoHS compliant to EU regulation.

## 3. Placement

Please pay attention to the placement and the PCB layout in your application design.

### 3.1. Pin Assignment

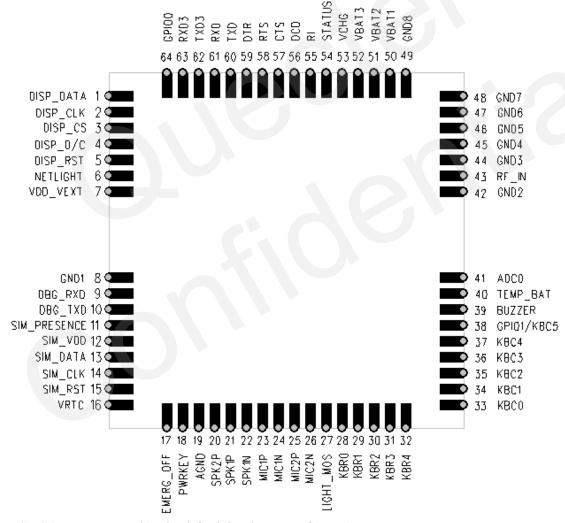

The pin assignment of the M10 module is shown in Figure 1. Placement of module should be carefully considered to make the RF\_IN pad as close as possible to antenna so as to reduce overall RF trace length. The longer the RF trace to antenna, the larger the RF insertion loss. In addition, please keep RF part and antenna from the system crystal and the audio part in host board as far as possible to reduce possible RF interference due to GSM transmission bursts from antenna and RF trace.

VCHG is not supported in the default hardware configuration.

Figure 1: Pin assignment

M10\_HD\_AN01\_V1.02

#### 3.2. Placement Recommendation

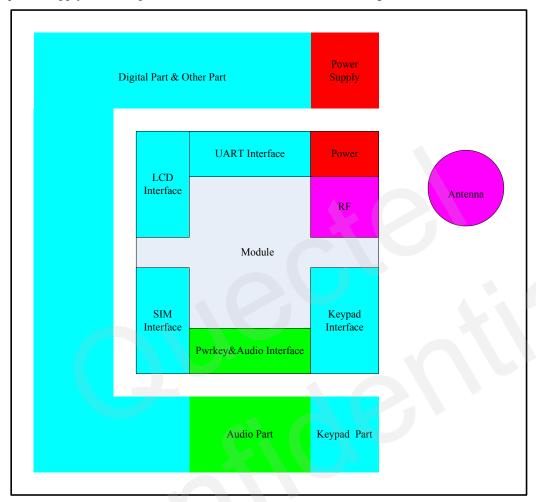

The analog part components such as microphone should be placed far away from antenna and power supply. General placement recommendation is shown in Figure 2.

Figure 2: Recommendation of placement

### 3.3. Placement Clearance

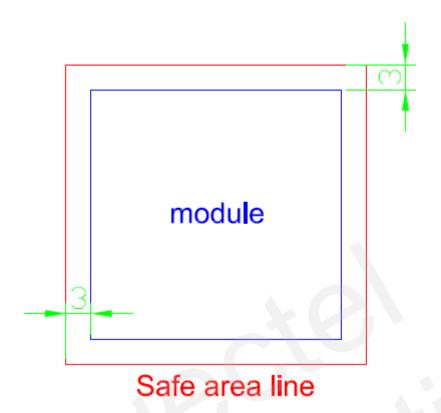

The module mounts with 64 SMT pads. For easy maintenance of this module and accessing to these pads, please keep a distance no less than 3mm between M10 and other components.

M10\_HD\_AN01\_V1.02 -9-

- 10 -

Figure 3: Placement clearance

# 4. Digital I/O Connection

If the voltage level of peripheral interface circuit does not match module interface, the power consumption of the system could increase, and could even cause the module damaged.

• Each digital I/O of the module operates in a 2.8V logic level inside the module. The voltage level of those digital interfaces connected to the module should match the electrical characteristics of the module listed in Table 3. Otherwise, a level shifter circuit must be inserted between the host and the module.

**Table 3: Digital I/O electrical characteristics**

| SYMBOL | MIN | MAX  | UNITS |

|--------|-----|------|-------|

| VIL    | 0   | 0.67 | V     |

| Vih    | 1.7 | 3.1  | V     |

| Vol    | 0   | 0.34 | V     |

| Voh    | 2.0 | 2.8  | V     |

• For direct connection between I/Os, please pay attention to I/Os' input or output configuration. If the I/O direction configuration conflicts with each other, the power consumption could increase, and the module could be very hot, and even be damaged. For example, it is forbidden that user's I/O outputs a low level while module's connected I/O outputs a high level.

# 5. VDD\_EXT & STATUS Pin

This pin is a power supply from a regulator inside the module which can power about 20mA of current. Do not use this pin to as indication of power-on and power-off. The STATUS pin can be used to judge whether module is power-on. In customer design, this pin can be connected to a GPIO of DTE or be used to drive an LED in order to judge module operation status. For more details, please refer to Chapter 3.4 in the document [1].

# 6. Serial Port and Debug Port

The TXD and RXD pins should be connected to host MCU. The DTR pin should be controlled to trigger SLEEP mode or wakeup the module. The RTS and CTS pins should be connected to the host MCU if hardware flow control is required.

The TXD, RXD, PWRKEY and GND pins can also be used for software upgrade and high-level parameters configuration. The DBG\_TXD and DBG\_RXD pins are only used for software debug. Please note that the PWRKEY pin should be pulled to low level when the M10 is being upgraded. For more detailed information on serial port design, please refer to document [2] and document[3].

Notes: It's recommended to connect the pins necessary for firmware upgrade to external interface.

# 7. SIM Card

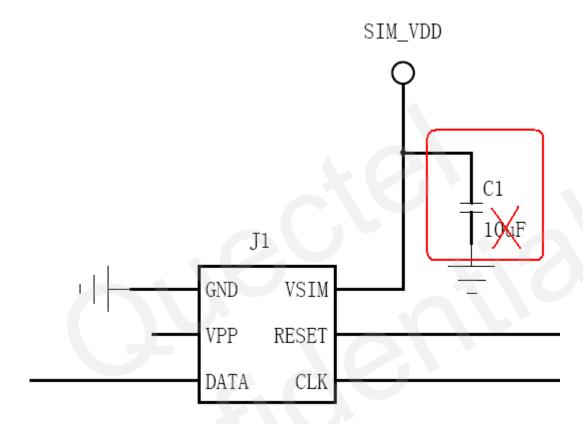

As shown in Figure 4, connecting a large volume capacitor such as 10uF in the SIM\_VDD line could lead to failure of detecting the SIM card. A capacitor between 100nF and 1uF is recommended.

Figure 4: Circuit of the SIM card

M10\_HD\_AN01\_V1.02 - 14 -

# 8. SLEEP Mode

The command AT+QSCLK can enable or disable SLEEP mode. When the SLEEP mode is enabled, pulling the DTR pin to high level would drive the module into SLEEP mode; and pulling the DTR pin to low level the module would exit from SLEEP mode.

## 9. Audio Trace

If possible, the audio trace should be placed in inner layer, and shielded by ground in the same layer and the upper and lower adjacent layers to prevent from RF interference. In addition, it is recommended to add as many via as possible between ground layers so as to reduce RF noise.

The AGND signal is usually used for AOUT2 channel to establish a single-end output with SPK2P. Do not pair GND with SPK2P to establish an audio output, otherwise TDD (Time Division Duplex) noise from power supply could occur in AOUT2. For more detailed information on audio design, please refer to document [3].

Figure 5: Audio trace routing example

M10\_HD\_AN01\_V1.02 - 16 -

## 10. RF Design Guide

Correct RF design is essential for RF performance such as TX power, RX sensitivity and harmonics. Following this RF design guide could benefit to improve the RF performance of customer's product.

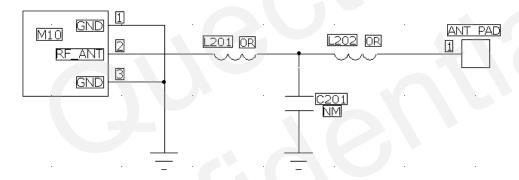

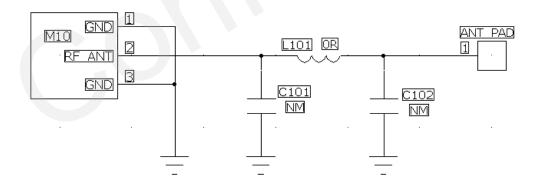

#### 10.1. Recommended Impedance Matching Circuit

The impedance of M10's RF\_ANT port is  $50\Omega$ . If the impedance of antenna is close to  $50\Omega$  in all working frequency bands, the antenna could be connected to the RF\_ANT port directly via  $50\Omega$  transmission line. But if the impedance of antenna is not close to  $50\Omega$ , a T-type or  $\pi$ -type matching circuit should be inserted between transmission line and antenna. The matching components should be placed as close as possible to the antenna's feed point.

Figure 6 and Figure 7 show the reference designs of T-type and  $\pi$ -type matching circuits.

Figure 6: T-type matching circuit

Figure 7:  $\pi$ -type matching circuit

*NOTE:* The impedance of traces in Bold type must be  $50\Omega$ .

M10 HD\_AN01\_V1.02 -17-

#### 10.2. Matched RF Transmission Line Design

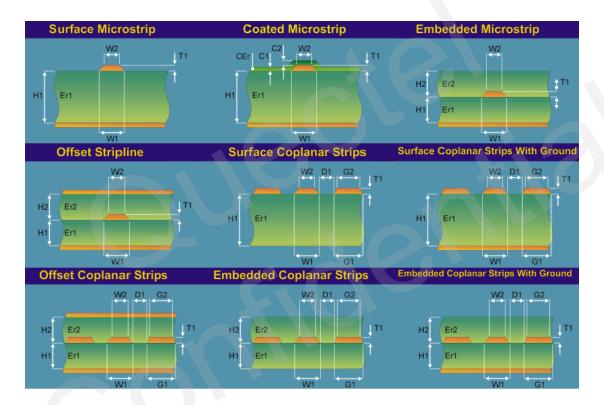

In PCB layout, a matched RF transmission line has a fixed characteristic impedance, which is called  $Z_0$ , from its source to its load. The source should have an internal resistance of  $Z_0$  and the resistance of matching load should close to  $Z_0$ .

Since the impedance of M10's RF\_ANT port is  $50\Omega$ , the impedance of the RF transmission line from this port to the antenna or the matching circuit should also be made to  $50\Omega$ .

More than twelve different types of transmission line can be created on a PCB simply by controlling trace geometry, and some of them are shown in Figure 8.

Figure 8: M10 RF ANT PCB layout

Customer may adopt one or certain types of them to design RF trace. Upon the demand of application design, the number of PCB layer can be different such as two and four. Each type of PCB has corresponding "stack-up". The "stack-up" is the name given to the order of the various etched copper foil and dielectric layers that are laminated together under pressure and heat to make a PCB.

Customer can calculate  $50\Omega$  RF trace width by EDA tools such as CITS or APPCAD, or send the "stack-up" to Quectel, and we can help to calculate it.

M10 HD\_AN01\_V1.02 -18-

#### 10.3. PCB Layout Consideration

PCB Layout is essential to the performance of customer's product. Here are some rules that should be followed:

#### Impedance control

Control the impedance of RF trace as close as possible to 50Ω. If the thickness between RF\_ANT pad and the ground layer is less than 0.4mm, it could significantly decrease the output power. Therefore, when they are too close, we strongly suggest removing the copper in the layer beneath the RF\_ANT pad. If RF trace routes to another layer, add GND via along with it to keep GND integral. The clearance between RF trace and ground plane in same layer should be at least twice the RF trace width.

### Make RF trace as short as possible

Place the module and the matching circuit near the antenna pad. Shorten the length of RF trace. Place the antenna PAD in the corner or at the edge of host board.

#### Protect RF trace

Avoid placing noise generating traces such as digital signal or clock line near RF trace in the same layer. Carefully route other traces in the layers adjacent to the RF trace, remember not to route in parallel with the RF trace. If possible, keep those traces far away from the RF trace.

An RF test point is located at the bottom side of M10 for manufacture purpose. The copper which is close to this test point in the top layer of customer's host board must be kept out or removed. No signal trace should be placed in the top layer and the second layer beneath this test point. The location of the test point and the size of removed copper are as Figure 9.

Figure 9: M10 bottom dimensions

M10 HD\_AN01\_V1.02 - 19 -

• Customer can use either antenna PAD or RF connector to connect the antenna. If antenna PAD is adopted, Figure 10 is a reference design for a four-layer PCB. Make the space on all layers beneath antenna pad keep-out. Place a ground PAD near the antenna PAD. The distance between GND PAD and antenna PAD can be around 1.8mm. The size of antenna PAD can be 1.8mm\*1.8mm, and the GND PAD should be a little bigger, e.g. 2.5mm\*2.5mm. Add several GND via near or on the GND PAD to reduce impedance from the GND PAD to the RF reference ground.

Figure 10: Reference PCB design with antenna pad in a four-layer PCB

If RF connector is adopted, place the RF connector close to module RF\_ANT, and add several ground via close to the GND PAD of RF connector. Figure 11 is the reference PCB design.

Figure 11: Reference PCB design with RF connector in a four-layer PCB

The stack-up of the four-layer PCB is shown in Table 4.

Table 4: Stack-up of the four-layer PCB

|        | Solder Mask        | 18.0 μm.                   |

|--------|--------------------|----------------------------|

|        | Chemical Gold      | 0.05 μm.                   |

|        | Electroless Nickel | 2.54 μm.                   |

|        | Copper Plating     | 13 μm.                     |

| LAYER1 | Copper             | 12.0 μm.                   |

|        | 1080LDP            | 200.0 μm standard-vias 1-4 |

| LAYER2 | Copper             | 18.0 μm.                   |

|        | Prepreg 2116       | 500.0 μm.                  |

| LAYER3 | Copper             | 18.0 μm.                   |

|        | 1080LDP            | 200.0 μm.                  |

| LAYER4 | Copper             | 12.0 μm.                   |

|        | Copper Plating     | 13 μm.                     |

|        | Electroless Nickel | 2.54 μm.                   |

|        | Chemical Gold      | 0.05 μm.                   |

|        | Solder Mask        | 18.0 μm.                   |

M10\_HD\_AN01\_V1.02 -21 -

# 11. The Recommended Ramp-soak-spike Reflow Profile

Figure 12: The recommended ramp-soak-spike reflow profile

Shanghai Quectel Wireless Solutions Co., Ltd.

Room 501, Building 9, No.99, TianZhou Road, Shanghai, China 200233 Tel: +86 21 5108 2965

Mail: info@quectel.com